国产EDA扎堆亮相,异构集成刷屏热议 世界半导体大会的集成电路设计风向标

世界半导体大会的集成电路设计专题论坛成为了全球产业与技术关注的焦点。两大核心趋势——国产EDA(电子设计自动化)工具的集中突破与异构集成的技术深化,构成了本次盛会的技术主旋律,深刻揭示了后摩尔时代芯片设计领域的关键演进路径。

国产EDA:从“点工具”到“全流程”,生态突围进行时

本届大会上,多家国内领先的EDA企业集中展示了最新研发成果,覆盖了从模拟电路设计、数字前端到后端物理实现、封装仿真乃至芯片制造良率提升等多个环节。与以往在个别“点工具”上取得突破不同,当前的展示更强调全流程解决方案的整合能力与对先进工艺节点的支持。

核心亮点包括:

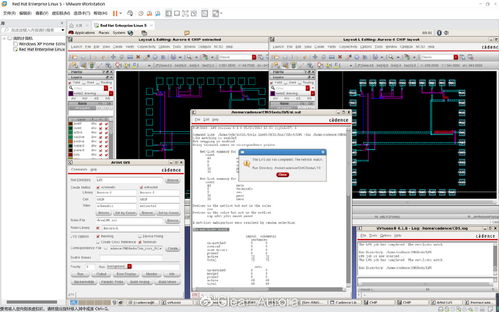

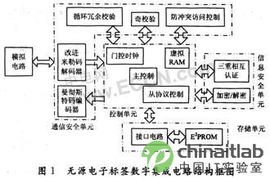

1. 全流程工具链雏形显现: 部分国产EDA平台已能够支撑特定领域的完整设计流程,例如在模拟/数模混合电路设计或特定工艺的物理设计方面,提供了从前端设计、仿真验证到版图生成的一体化工具集,显著降低了设计门槛和工具切换成本。

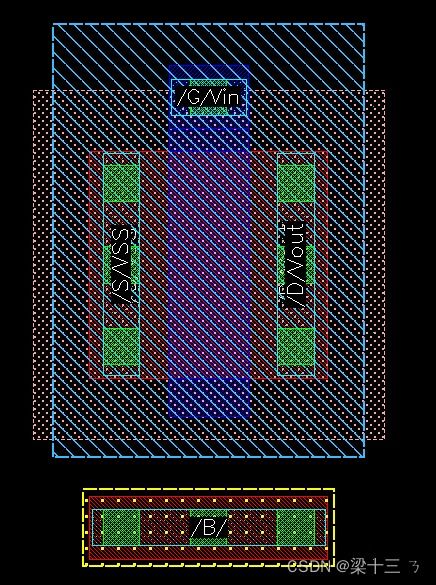

2. 与先进工艺和封装协同: 新一代工具加强了对FinFET等先进工艺的适配,并开始深度集成面向Chiplet(芯粒)和异构集成的设计、仿真与验证模块,体现了从跟随到面向未来需求的转变。

3. 产学研用协同深化: 大会期间,多家EDA公司与头部芯片设计企业、晶圆厂及高校签署了深度合作协议,旨在通过实际项目打磨工具,加速迭代,共同构建更健壮的国产EDA应用生态。

业界共识认为,国产EDA正从“可用”向“好用、易用”阶段迈进,但挑战依然存在,包括在超大规模数字电路设计、尖端工艺PDK(工艺设计套件)的完整支持以及与全球最复杂IP生态的深度融合等方面,仍需持续攻坚。

异构集成:超越摩尔定律的“C位”技术

如果说EDA是设计之“笔”,那么异构集成则代表了设计思想之“魂”。本次大会上,异构集成技术占据了技术讨论的绝对“C位”,成为应对算力需求爆炸、功能多样化与能效挑战的核心答案。

讨论焦点集中在以下几个方面:

1. Chiplet(芯粒)互连与标准: 如何实现不同工艺节点、不同功能、不同来源(甚至不同厂商)的Chiplet之间的高速、高带宽、低功耗互连,是技术关键。大会深入探讨了UCIe(通用芯粒互连技术)等新兴开放标准的进展、挑战与生态建设路径。国内产业界也在积极推动相关标准的研究与制定。

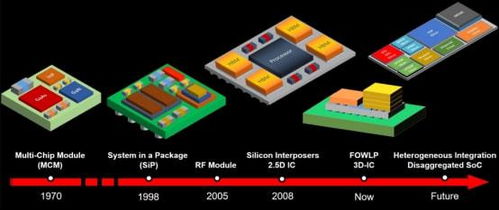

2. 先进封装技术驱动: 异构集成的实现高度依赖于2.5D/3D封装、硅通孔(TSV)、扇出型(Fan-Out)等先进封装技术。封装厂与设计公司的协同设计(Co-Design)成为必然趋势,EDA工具需要为此提供从架构探索、物理实现到热、应力、信号完整性分析的全面支持。

3. 系统级架构创新: 异构集成不仅仅是物理上的堆叠,更是系统架构的革新。设计思路从单一SoC(系统级芯片)转向基于芯粒的“乐高式”系统级封装(SiP),如何在不同计算单元(CPU、GPU、NPU、FPGA等)之间实现高效的存算一体、数据调度与任务分配,是提升整体系统性能的关键。

4. 设计方法论变革: 传统的芯片设计流程正被重构。系统架构师、芯片设计师、封装工程师、软件开发者需要更早、更紧密地协作。新的设计工具链和验证方法学(如芯片-封装-系统协同仿真)亟待完善。

融合与展望:设计、工具与生态的共舞

世界半导体大会清晰地表明,集成电路设计的是国产EDA工具的自主创新与异构集成的系统级突破两条主线深度融合、相互促进的进程。

- EDA工具必须拥抱异构集成的复杂性,发展出能够处理多物理域、多尺度、多工艺协同设计与分析的下一代平台。

- 异构集成技术的广泛应用与成本降低,反过来也离不开强大、灵活且成本可控的EDA工具支持。

- 开放合作的产业生态是成败的关键。从芯粒接口标准、IP复用、到设计与制造服务的协同,构建一个全球或区域性的、基于开放标准的异构集成生态系统,将是整个产业面临的共同课题。

结论: 本届世界半导体大会为集成电路设计领域描绘了一幅清晰的图景:在后摩尔时代,通过国产EDA的全流程攻坚与异构集成的系统级创新“双轮驱动”,中国集成电路产业正致力于在基础工具和前沿设计方法学上构建核心竞争力,以期在全球半导体产业的新一轮格局重塑中占据更主动的位置。前路挑战艰巨,但方向已然明确,步伐正在加速。

如若转载,请注明出处:http://www.kxkdqntm.com/product/59.html

更新时间:2026-04-18 08:38:49